深入了解台积电的 3 纳米节点和 FinFlex 技术

据台湾媒体报道,台积电 (TSMC) 有望在 9 月推出期待已久的 3 纳米工艺节点,而苹果将成为其首个 3 纳米客户,采用台积电制造的 M2 Pro 处理器在今年晚些时候推出的 Mac 机器中。根据DigiTimes发表的报道,其他承诺在台积电 3 纳米节点制造芯片的半导体供应商包括 AMD、博通、英特尔、联发科、英伟达和高通。

这显示了三星代工的强大优势,三星代工在今年早些时候成为焦点,当时它声称要大规模生产 3 纳米处理器。然而,众所周知,三星代工除了自己的 Exynos 处理器外,唯一值得注意的客户是高通的 Snapdragon 智能手机处理器,它正在与三星的 Exynos 智能手机处理器直接竞争。

此外,与三星在其 3 纳米节点转向新的全沿栅极 (GAA) 技术不同,台积电决定在 3 纳米制造工艺中继续使用 FinFET 技术,而不是在即将到来的 2 纳米节点上转向 GAA过程。GAA 制造技术凭借其高导电性增强了芯片性能。

贸易媒体也有关于 3 纳米制造工艺即将延迟到来的猜测,台积电声称该工艺将在 2022 年 9 月前准备就绪。有媒体传言称,台积电的 3 纳米计划可能会因英特尔的推迟而推迟。一些即将推出的处理器的设计更改。最终,台湾领先的半导体代工厂商得以坚持原定计划,实现了 2022 年下半年开始生产 3 纳米的目标。

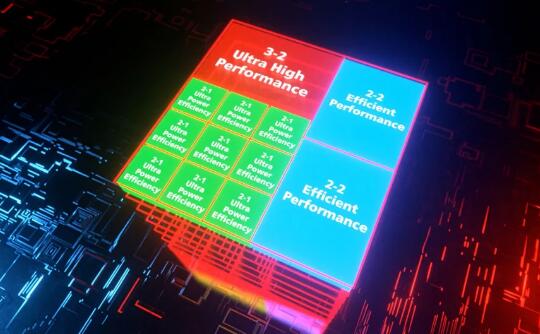

图 1台积电的 3 纳米工艺节点基于 FinFlex 技术,该技术为芯片设计人员提供了在提高性能、功率或芯片面积方面的灵活性和对其芯片设计的控制。资料来源:台积电

FinFlex技术

台积电的 3 纳米工艺节点(称为 N3)采用FinFlex技术,允许芯片设计人员在一个模块内混合和匹配不同类型的标准单元,以准确优化性能、功耗和面积 (PPA)。这一新功能特别有利于制造复杂的芯片设计,例如具有大量内核的 CPU 和 GPU。

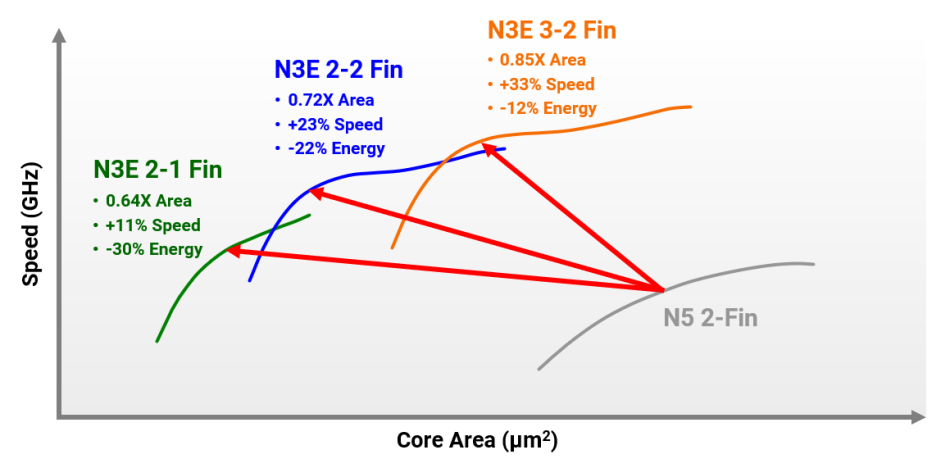

与台积电的 5 纳米节点(通常称为 N5)相比,N3 节点的初始版本预计将提供 10% 至 15% 的性能提升,将功耗降低 25% 至 30%,并将逻辑密度提高约 1.6次。但是,对于某些芯片设计,它的良率可能低于预期。台积电计划发布具有改进工艺的 N3E 节点,其晶体管密度略低,但将支持大批量制造 (HVM)。

图 2在 N3E 工艺中,2-1 Fin 可降低功耗和泄漏,而 2-2 Fin 可提高性能。2-3 Fin 可提高时钟频率以满足更大的计算需求。资料来源:台积电

最终,台积电将在其 3 纳米节点系列中添加 N3P、N3S 和 N3X 版本。在这里,值得注意的是,位于台湾新竹的半导体工厂之前提供了同一节点的不同版本。然而,这一次,它基于新的 FinFlex 技术,允许芯片供应商定制他们的设计,以提高 3 纳米芯片不同领域的性能。换句话说,3nm 制造工艺将在每个晶体管的鳍片数量方面提供不同的变化。

虽然 3 纳米工艺技术和原始节点将于下个月启动,但这些变体将在 2023 年和 2024 年上线。